# 15. Hardware Security (Spectre and Meltdown Attacks)

Blase Ur and Grant Ho February 26<sup>th</sup>, 2024 CMSC 23200

Attacks that exploit processor vulnerabilities

Can leak sensitive data

Relatively hard to mitigate

Lots of media attention

- Memory isolation: Processes should only be able to read their own memory

- Virtual (paged) memory

- Protected memory / Protection domains

- CPUs have a relatively small, very fast cache

- Loading uncached data can take >100 CPU cycles

- Out-of-order execution: Order of processing in CPU can differ from the order in code

- Instructions are much faster than memory access; you might be waiting for operands to be read from memory

- Instructions retire (return to the system) in order even if they executed out of order

- There might be a conditional branch in the instructions

- Speculative execution: Rather than waiting to determine which branch of a conditional to take, go ahead anyway

- Predictive execution: Guess which branch to take

- Eager execution: Take both branches

- When the CPU realizes that the branch was misspeculatively executed, it tries to eliminate the effects

- A core idea underlying Spectre/Meltdown: The results of the instruction(s) that were mistakenly speculatively executed will be cached in the CPU [yikes!]

# Example (not problematic as written)

Consider the code sample below. If <a href="mailto:arr1->length">arr1->length</a> is uncached, the processor can speculatively load data from <a href="mailto:arr1->data[untrusted\_offset\_from\_caller]">arr1->data[untrusted\_offset\_from\_caller]</a>. This is an out-of-bounds read. That should not matter because the processor will effectively roll back the execution state when the branch has executed; none of the speculatively executed instructions will retire (e.g. cause registers etc. to be affected).

```

struct array {

unsigned long length;

unsigned char data[];

};

struct array *arr1 = ...;

unsigned long untrusted_offset_from_caller = ...;

if (untrusted_offset_from_caller < arr1->length) {

unsigned char value = arr1->data[untrusted_offset_from_caller];

...

}

```

# Example (really bad!!!)

However, in the following code sample, there's an issue. If <a href="arr1->length">arr2->data[0x200]</a> and <a href="arr2->data[0x300]">are not cached, but all other accessed data is, and the branch conditions are predicted as true, the processor can do the following speculatively before <a href="arr1->length">arr1->length</a> has been loaded and the execution is re-steered:

- load value = arr1->data[untrusted offset from caller]

- start a load from a data-dependent offset in arr2->data, loading the corresponding cache line into the L1 cache

# Example (really bad!!!)

```

struct array {

unsigned long length;

unsigned char data[];

struct array *arr1 = ...; /* small array */

struct array *arr2 = ...; /* array of size 0x400 */

/* > 0 \times 400 (OUT OF BOUNDS!) */

unsigned long untrusted offset from caller = ...;

if (untrusted offset from caller < arr1->length) {

unsigned char value = arr1->data[untrusted offset from caller];

unsigned long index2 = ((value \& 1) * 0x100) + 0x200;

if (index2 < arr2->length) {

unsigned char value2 = arr2->data[index2];

```

# Example (really bad!!!)

After the execution has been returned to the non-speculative path because the processor has noticed that <a href="mailto:untrusted\_offset\_from\_caller">untrusted\_offset\_from\_caller</a> is bigger than <a href="mailto:arr1->length">arr1->length</a>, the cache line containing <a href="mailto:arr2->data[index2]">arr2->data[index2]</a> stays in the L1 cache. By measuring the time required to load <a href="mailto:arr2->data[0x200]">arr2->data[0x200]</a> and <a href="mailto:arr2->data[0x300]</a>, an attacker can then determine whether the value of <a href="mailto:index2">index2</a> during speculative execution was 0x200 or 0x300 - which discloses whether <a href="mailto:arr1->data[untrusted\_offset\_from\_caller]">arr1->data[untrusted\_offset\_from\_caller]</a> &1 is 0 or 1.

# Spectre: Key Idea

- Use branch prediction as on the previous slide

- Conducting a timing side-channel attack on the cache

- Determine the value of interest based on the speed with which it returns

- Spectre allows you to read any memory <u>from your</u> <u>process</u> for nearly every CPU

## Spectre: Exploitation Scenarios

- Leaking browser memory

- JavaScript (e.g., in an ad) can run Spectre

- Can leak browser cache, session key, other site data

### Spectre: Exploitation Scenarios

"But today, Voisin said he discovered new Spectre exploits—one for Windows and one for Linux—different from the ones before. In particular, Voisin said he found a Linux Spectre exploit capable of dumping the contents of **/etc/shadow**, a Linux file that stores details on OS user accounts"

## Meltdown: Key Ideas

- Attempt instruction with memory operand (Base+A), where A is a value forbidden to the process

- 2. The CPU schedules a privilege check and the actual access

- 3. The privilege check fails, but due to speculative execution, the access has already run and the result has been cached

- Conduct a timing attack reading memory at the address (Base+A) for all possible values of A. The one that ran will return faster

# Meltdown: Impact

Meltdown allows you to read **any memory in the address space** (even from other processes) but only on some (unpatched) Intel/ARM CPUs

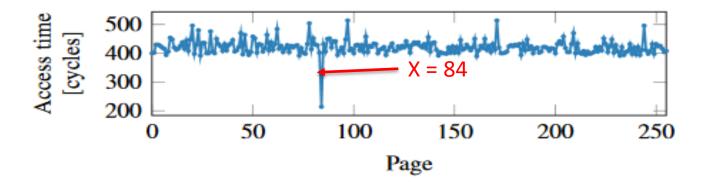

# Meltdown: Timing Side Channel

- Now the attacker reads each page of probe array

- 255 of them will be slow

- The X<sup>th</sup> page will be faster (it is cached!)

- We get the value of X using cache-timing side channel

Figure 4: Even if a memory location is only accessed during out-of-order execution, it remains cached. Iterating over the 256 pages of probe\_array shows one cache hit, exactly on the page that was accessed during the out-of-order execution.

# Meltdown: Mitigation

- KAISER/KPTI (kernel page table isolation)

- Remove kernel memory mapping in user space processes

- Has non-negligible performance impact

- Some kernel memory still needs to be mapped